MoneyDJ新聞 2025-11-25 17:12:52 新聞中心 發佈

根據集邦科技(TrendForce)最新研究指出,AI HPC(高效能運算)對異質整合的需求將仰賴先進封裝來達成,其中關鍵技術即是台積電(2330)的CoWoS解決方案。然而,隨著雲端服務業者(CSP)加速自研ASIC,為整合更多複雜功能的晶片,對封裝面積需求不斷擴大,已有CSP開始考慮從台積電的CoWoS方案,轉向Intel的EMIB技術。

根據集邦科技(TrendForce)最新研究指出,AI HPC(高效能運算)對異質整合的需求將仰賴先進封裝來達成,其中關鍵技術即是台積電(2330)的CoWoS解決方案。然而,隨著雲端服務業者(CSP)加速自研ASIC,為整合更多複雜功能的晶片,對封裝面積需求不斷擴大,已有CSP開始考慮從台積電的CoWoS方案,轉向Intel的EMIB技術。

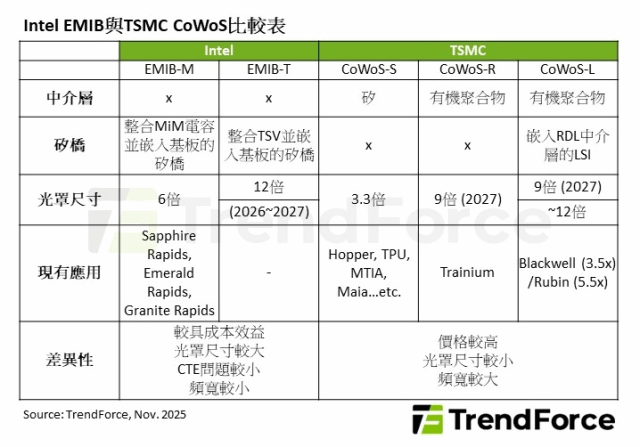

集邦表示,CoWoS方案將主運算邏輯晶片、記憶體、I/O等不同功能的晶片,以中介層(Interposer)方式連結,並固定在基板上,目前已發展出CoWoS-S、CoWoS-R與CoWoS-L等技術。隨著NVIDIA Blackwell平台於今(2025)年進入規模量產,目前市場需求已高度傾向內嵌矽中介層的CoWoS-L,同時NVIDIA下世代的Rubin亦將採用,並進一步推升光罩尺寸。

AI HPC需求旺盛導致CoWoS面臨產能短缺、光罩尺寸限制,以及價格高昂等問題。集邦觀察,除了CoWoS多數產能長期被NVIDIA GPU占據、其他客戶遭排擠,封裝尺寸以及地緣政治下的美國在地製造需求,也促使Google、Meta等北美CSP開始積極與Intel接洽EMIB解決方案。

集邦指出,EMIB相較CoWoS擁有數項優勢,首先是結構簡化,EMIB捨棄昂貴且大面積的中介層,直接將晶片使用內嵌在載板的矽橋(Bridge)方式進行互連,簡化整體結構,相對於CoWoS良率更高。其次,則是熱膨脹係數(Coefficient of Thermal Expansion, CTE)問題較小,由於EMIB只在晶片邊緣嵌矽橋,整體矽比例低,因此矽與基板的接觸區域少,導致熱膨脹係數不匹配的問題較小,較不易產生封裝翹曲與可靠度挑戰。

EMIB在封裝尺寸也較具優勢,相較於CoWoS-S僅能達到3.3倍光罩尺寸、CoWoS-L目前發展至3.5倍,預計在2027年達9倍;EMIB-M已可提供6倍光罩尺寸,並預計2026到2027年可支援到8倍至12倍。在價格部分,因EMIB捨棄價格高昂的中介層,能為AI客戶提供更具成本優勢的解決方案。

然而,EMIB技術受限於矽橋面積與佈線密度,可提供的互連頻寬相對較低,訊號傳輸距離較長,並有延遲性略高的問題。因此,目前僅ASIC客戶較積極在評估洽談導入。

集邦指出,Intel自設立獨立的晶圓代工服務(Intel Foundry Services, IFS)事業群,耕耘EMIB先進封裝技術多年,已應用至自家server CPU平台Sapphire Rapids和Granite Rapids等。隨著Google決議在2027年TPUv9導入EMIB試用,Meta亦積極評估規劃用於其MTIA產品,EMIB技術有望為IFS業務帶來重大進展。至於NVIDIA、AMD等對於頻寬、傳輸速度及低延遲需求較高的GPU供應商,仍將以CoWoS為主要封裝解決方案。

(圖片來源:TrendForce)